### The New Frontier of System Design How to Efficiently Conquer All Your Design Needs

## **The Designer's Environment**

# challenges

- Meeting functionality specifications

- Meeting power targets

- Meeting performance targets

- Staying on schedule and on budget

- Needing to design different products high end, low cost

# starting a project

- Specifications

- Cost target

- Schedule requirements

## But Do You Really Know....

## what's behind the scenes?

- Will marketing make last-minute changes to the specification?

- Will the competitive landscape change?

- New entrants

- Disruptive technologies

- Will customer requirements change?

......Will you be able to meet your schedule and budget?

## What If...

- You had the flexibility to react to market changes and evolving specifications while still meeting your schedule?

- You could lower your development cost, yet maintain your differentiation?

- You could significantly increase your system performance while staying within the power budget?

- You could move from prototyping to low-cost production in a risk-free and cost-effective way?

- You could use one development software tool for all your design needs?

## the perfect scenario

## What If...

- You had the flexibility to react to market changes and evolving specifications while still meeting your schedule?

- You could lower your development cost, yet maintain your differentiation?

- You could significantly increase your system performance while staying within the power budget?

- You could move from prototyping to low-cost production in a risk-free and cost-effective way?

- You could use one development software tool for all your design needs?

© 2007 Altera Corporation—Public

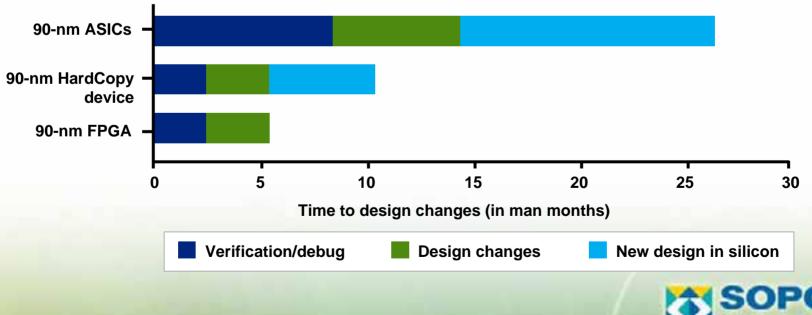

## **Timeline for Design Changes**

|                             | 90-nm FPGA* | 90-nm HardCopy <sup>®</sup><br>Device* | 90-nm ASICs* |

|-----------------------------|-------------|----------------------------------------|--------------|

| Verification/Debug          | 2           | 2                                      | 8            |

| Design Changes              | 3           | 3                                      | 6            |

| New Design in Silicon       | 0           | 5                                      | 12           |

| Accomodating design changes | ~5          | ~10                                    | ~27          |

\* All values are in man months

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

7

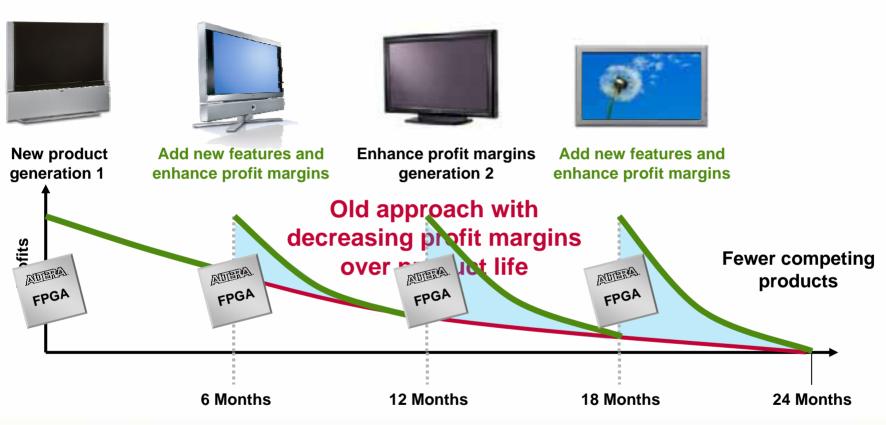

## **Solving the Development Dilemma**

### Design a Single Platform for Multiple Sizes and Resolutions

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

8

## What If...

- You had the flexibility to react to market changes and evolving specifications while still meeting your schedule?

- You could lower your development cost, yet maintain your differentiation?

- You could significantly increase your system performance while staying within the power budget?

- You could move from prototyping to low-cost production in a risk-free and cost-effective way?

- You could use one development software tool for all your design needs?

## development cost

© 2007 Altera Corporation—Public

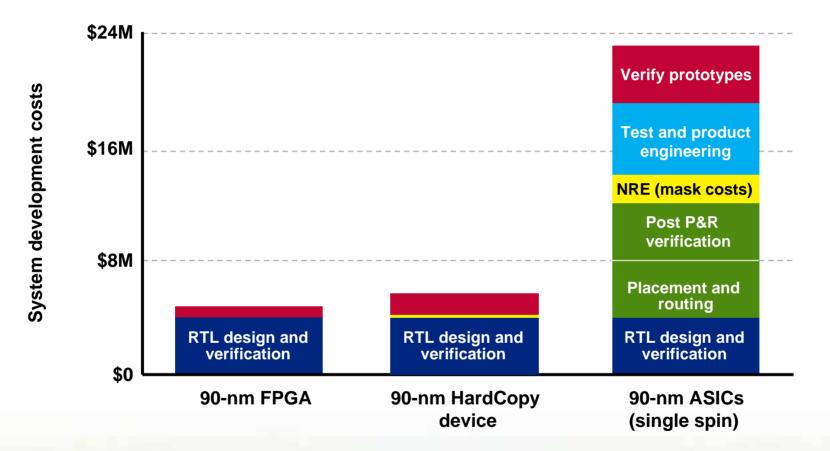

## **System Development Cost**

75% Lower System Development Costs With FPGAs

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

10

## What If...

- You had the flexibility to react to market changes and evolving specifications while still meeting your schedule?

- You could lower your development cost, yet maintain your differentiation?

- You could significantly increase your system performance while staying within the power budget?

- You could move from prototyping to low-cost production in a risk-free and cost-effective way?

- You could use one development software tool for all your design needs?

## performance/power

© 2007 Altera Corporation—Public

11

## Stratix III FPGAs: Power & Performance Advantage

- Stratix<sup>®</sup> III performance advantage

- 25 percent faster than nearest competing FPGAs

- Maximum internal clock speed: 600 MHz

- On-chip RAM: 600 MHz

- Digital signal processing (DSP) blocks

@ 550 MHz

- Supports 400-MHz DDR3 and DDR2 external memory

- Supports 1.25-Gbps LVDS

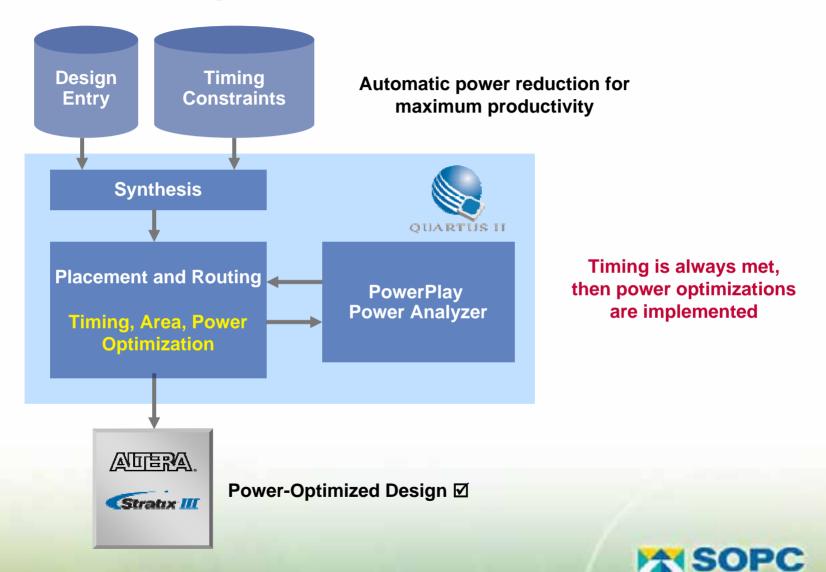

- Stratix III power advantage

- Programmable Power Technology

- Selectable core voltage

- Quartus<sup>®</sup> II PowerPlay power analysis and optimization tool

<sup>© 2007</sup> Altera Corporation—Public

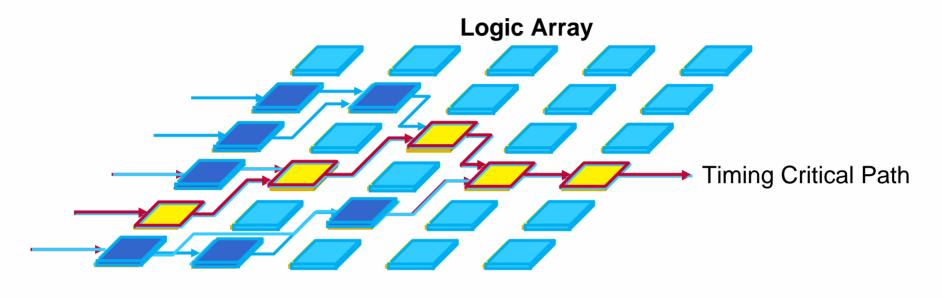

## **Programmable Power Technology**

High-Speed Logic

Low-Power Logic

Unused Low-Power Logic

## Performance Where You Need It, Lowest Power Everywhere Else

© 2007 Altera Corporation—Public

## **Automated by Quartus II Software**

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

14

## What If...

- You had the flexibility to react to market changes and evolving specifications while still meeting your schedule?

- You could lower your development cost, yet maintain your differentiation?

- You could significantly increase your system performance while staying within the power budget?

- You could move from prototyping to low-cost production in a risk-free and cost-effective way?

- You could use one development software tool for all your design needs?

© 2007 Altera Corporation—Public

## **Benefits of a Structured ASIC**

Standard cell ASIC: All layers are custom

Structured ASIC: Customization through top layers

Full set of masks for standard-cell ASIC

Base layer

## **Structured ASICs Minimize NRE and Turnaround Times**

© 2007 Altera Corporation—Public

## **HardCopy Structured ASICs**

- Advanced process (90 nm) delivers dramatically lower cost

- \$15 for 1M ASIC gates

- Up to 90% cost reduction

- Dramatic power reduction

- Up to 90% lower static power

- Up to 50% lower active power

- Up to 2.2M ASIC gates

- Seamless migration from Stratix series FPGA

HARDCOPF"II

## Faster Time-to-Market, Period

#### HardCopy development

#### \*With in-system verification

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

18

## What If...

- You had the flexibility to react to market changes and evolving specifications while still meeting your schedule?

- You could lower your development cost, yet maintain your differentiation?

- You could significantly increase your system performance while staying within the power budget?

- You could move from prototyping to low-cost production in a risk-free and cost-effective way?

- You could use one development software tool for all your design needs?

© 2007 Altera Corporation—Public

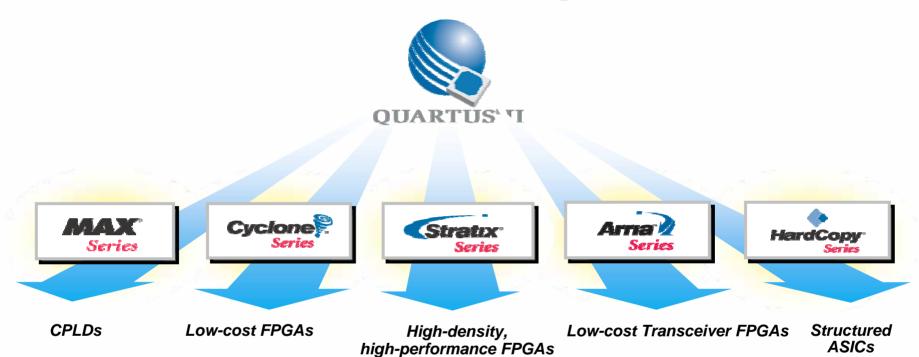

## **Quartus II Design Software**

- Everything you need to design for Altera<sup>®</sup> programmable logic devices

- #1 design software for performance and productivity

- Only complete development package supporting FPGA, CPLD, and structured ASICs

- Delivering fastest time to market

- Easiest to use

- Best-in-class technology

- Partnerships with industry leaders

#### Easiest Path From Design Ideas to Reality

© 2007 Altera Corporation—Public

## **One Tool for All Your Design Needs**

#### Low Development Cost. Improved Productivity

# productivity

© 2007 Altera Corporation—Public

## **MAX II Devices: CPLDs for Simple Applications**

- Innovative CPLD architecture delivers the lowest cost

- Cost-saving features

- 8-Kbit user flash memory

- Built-In voltage regulator

- On-chip oscillator

- Real-time in-system programming

- Non-volatile, instant-on

- 1/10<sup>th</sup> the power of previous MAX<sup>®</sup> devices

- Supports 3.3-, 2.5- and 1.8-V supply voltages

- Supported by Quartus II software

#### © 2007 Altera Corporation—Public

## **MAX II Target Applications**

- Interface bridging

- Bus protocol translation

- Serial-to-parallel data conversion

- System configuration

- ASIC/ASSP/FPGA configuration management

- Flash controller

- I/O expansion

- Control signal distribution

- Address decoding

- LED activity control

- Power-up sequencing

- Multi-voltage system power-up management

- System reset and chip select generation

© 2007 Altera Corporation—Public

## Cyclone III Low-Cost FPGAs for High-Volume Designs

- Low power

- TSMC 65-nm low-power (LP) process

- Quartus II software power-aware design flow

- 120K logic elements (LEs) under ½ W static

- High functionality

- Densities ranging from 5K to 120K LEs

- Up to 4 Mbits of embedded memory

- Up to 288 embedded multipliers for DSP

- Low cost

- First low-cost 65-nm FPGA

- Free Quartus II Web Edition software

- Prices starting as low as \$4.00

## **Turn Your Ideas Into Revenue Faster**

High Functionality

Low Cost

© 2007 Altera Corporation—Public

## Stratix II GX FPGAs for High-End Transceiver Designs

- Up to 20 transceivers operating between 600 Mbps and 6.375 Gbps

- Lowest-power FPGA with embedded transceivers

- Best-in-class signal integrity solution includes pre-emphasis and equalization

- Complete protocol solution including software support, intellectual property, system models, and reference designs

### **Transceivers With Optimal Signal Integrity**

## **Complete Protocol Solutions**

- Hard protocol intellectual property (IP), IP functions, reference designs

- Signal integrity modeling

- Protocol-specific development boards

PCI Express and SDI

- Evaluation board

- Compliance testing

- System validation reports

- Characterization reports

- Supported by Quartus II software

## **Dramatically Increase Ease of Design**

© 2007 Altera Corporation—Public

## Arria GX FPGAs for Low-Cost Transceiver Designs

- Risk-free, low-cost, transceiverbased FPGA family

- Support for mainstream protocols at 1.25 and 2.5 Gbps

- PCI Express (x1 and x4)

- Gigabit Ethernet

- Serial RapidIO<sup>®</sup> (1x and 4x)

- 5 family members ranging from 21,580 to 90,220 logic elements with up to 4.5 Mbits of memory and 12 transceivers

- 50K LEs for \$50 (25Ku)

- Supported by Quartus II software

| Device   | Transceiver<br>channels | Equivalent<br>logic<br>elements |  |

|----------|-------------------------|---------------------------------|--|

| EP1AGX20 | 4                       | 21,582                          |  |

| EP1AGX35 | 4                       | 33,514                          |  |

|          | 8                       |                                 |  |

| EP1AGX50 | 4                       | 50,165                          |  |

|          | 8                       |                                 |  |

| EP1AGX60 | 4                       | 60,108                          |  |

|          | 8                       |                                 |  |

|          | 12                      |                                 |  |

| EP1AGX90 | 12                      | 90,220                          |  |

© 2007 Altera Corporation—Public

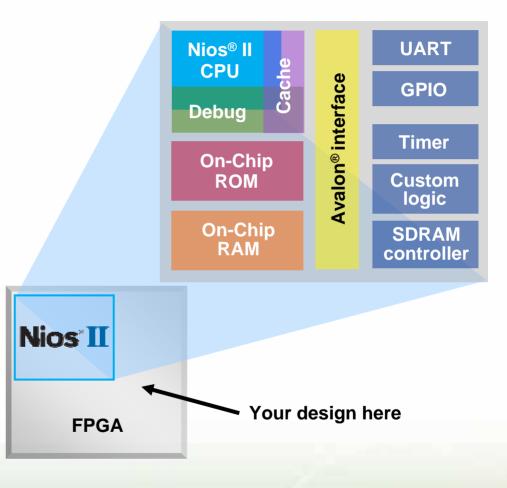

## **Nios II Processor Overview**

- Family of configurable 32-bit RISC processors

- Automated processor configuration and integration of peripherals via SOPC Builder

- Integrate custom logic to add custom features and boost performance

- Performance up to 300 DMIPs (/f, Stratix III FPGA)

- Cost as low as 25¢ of logic (/e, Cyclone III FPGA)

© 2007 Altera Corporation—Public

## Why 20K+ Developers Choose Nios II **Processors**

- Custom fit to users' application

- Fills gaps inherent in off-the-shelf devices

- Abundant IP

- Allows users to use their own innovation

- Works with all Altera FPGA devices

- Low-cost, high-density, transceivers

- Structured ASIC (lowest cost)

- Scalable performance

- Multi-core

- Custom instructions

- Hardware accelerators

- Deliver the right product at the right price in the shortest time

- From concept to system in minutes

29

# Why Altera: End-Market Focus to Align with Customers

Consumer Broadcast Automotive

Entertainment Broadband Audio/video Video display

#### **Broadcast**

Studio Satellite Broadcasting

#### Automotive Navigation

Entertainment

Test, Measurement and Medical

Instrumentation Medical Test equipment Manufacturing

**Communications**

Wireless Cellular Basestations Wireless LAN

Networking Switches Routers

Wireline Optical

Metro Access Military and Industrial

Military Secure comm. Radar Guidance and control

Security and Energy Management

Card readers Control systems ATM Computer and Storage

Computers Servers Mainframe

Storage

RAID San

Office Automation Copiers Printers MFP

© 2007 Altera Corporation—Public

## **Broadcast Value Proposition**

#### Quality, affordability, productivity

- Solutions and kits: defined by customer partners, characterized and proven, facilitates adoption, system integration and studio/headend interoperability

- Devices: superior performance, lower power and higher integration ideal for broadcast equipment needs

- Tools: multimedia framework, open interfaces \_ and Quartus II provides ease of use and higher productivity

1080p processing Audio SRC Triple-rate SDI MPEG-2 Format Conversion  $H_{264}$ Video/IP

Studios Contribution

Head-ends Distribution

#### Today's recognized FPGA vendor of choice for Broadcast

© 2007 Altera Corporation—Public

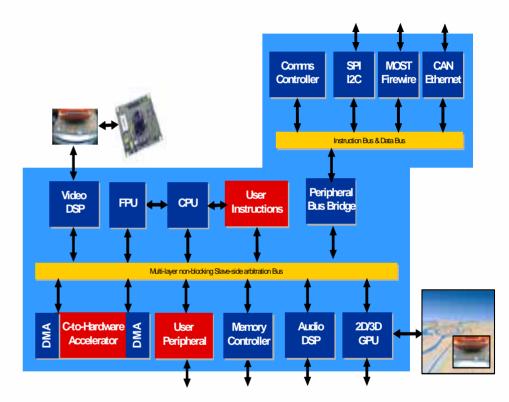

## **Automotive Value Proposition**

- Flexible microcontroller based infotainment system

- Enables comprehensive design methodology by incorporating hardware, IP, and software onto a single platform

- Reduces development time at customers

- Fully scalable and cost effective platform

- Seamless ASIC migration

- HardCopy device with fixed content (equivalent to ASSP)

Target Applications: Next generation car Infotainment and telematics systems

© 2007 Altera Corporation—Public

## With Altera You Can..

# face your challenges

- Business and technical goals

- Functionality specifications

- Power targets

- Performance targets

- Schedule and budget requirements

- All of your design needs, from high end to low cost

© 2007 Altera Corporation—Public

## **Altera: The Perfect Partner**

- Corporate strategy: Customer Productivity; Risk Reduction

- Comprehensive product portfolio

- CPLDs, FPGAs, and structured ASICs

- Extensive IP portfolio, including Nios II processor

- One design tool for all your design needs

- History of operational excellence

- 13-year sole partnership with TSMC, world's #1 foundry

- First time right silicon; risk reduction for our customers

#### Worldwide support

- Online support at www.altera.com

- 24-hour customer service and support

- Service centers in China, Japan, Europe, USA

- Ecosystem

- Partnership with best-in-class EDA, IP, and supply chain vendors

# high productivity: low risk

© 2007 Altera Corporation—Public